德国

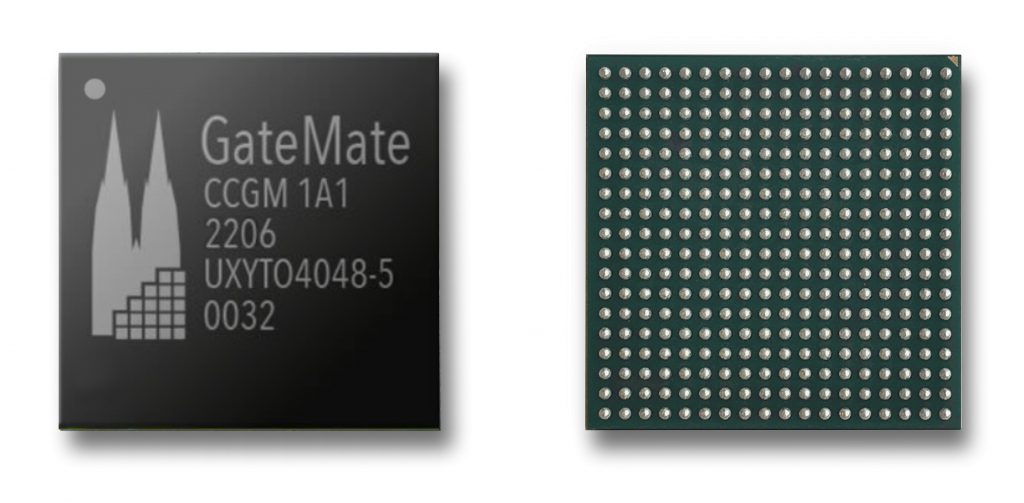

的GateMateTM芯片FPGA的科隆AG)地址所有应用程序要求中小规模的FPGA。逻辑能力、功耗、包大小和PCB兼容性是最好的。GateMateTMfpga将这些特性与最低成本在工业制造的设备适合大学项目的高容量的应用程序。因为优秀的电路大小/成本比率,新的应用程序现在可以使用fpga的好处。

所有这些都是基于一本小说FPGA架构结合CPE与智能路由引擎可编程元素。CPE的体系结构允许一个有效的建设任意份乘数。记忆意识到应用程序可以使用块公羊与宽度为1到80位。

通用IOs (GPIOs)可以使用不同的电压等级从1.2到2.5伏特。所有GPIOs可以配置为单端或LVDS差分对。此外高速并行转换器接口可用。

FPGA设计合成使用Yosys框架。科隆自由芯片P&R-software生成FPGA比特流。

静态时序分析(STA)也提供了关键路径的证据和执行设计的整体性能。设计可以用Verilog网表模拟和自卫队定时提取。

使用Globalfoundries设备制造TM28 nm SLP超级低功率)的过程。由于制造业在欧洲,没有危险的贸易限制或高税收。

小说CPE架构

低功耗

特性

包

的GateMateTM评估板是一个功能丰富,CCGM1A1现成的开发平台。

作为参考设计和直接进入应用程序开发。用户应用程序可以根据每个银行可用六的I / O。附加额外的硬件是一个微风由于Pmod连接器:他们允许访问各种外围板,包括电机控制器、传感器、显示器和更多。

•6 I / O银行+使用SPI / JTAG信号

•两个标准12-pin PmodTM连接器

•5 Gb / s并行转换器通过SMA连接器

•访问所有专门的时钟输入

•配置通过Flash, USB或JTAG

记忆:

•64 Mbit Quad-I / O SPI闪光

•两船上HyperBus记忆(HyperRAM / HyperFlash)

力量:

•游览器核心和I / O的电压